Intel ‘Lakefield’ is a mobile System on Chip (SoC) CPU design that was first outlined in 2018 but hasn’t yet seen its debut. However, a recently leaked slide says that these x86 integrated circuits, along with Intel Tiger Lake mobile processors, should be hitting the market in September or October 2020.

The leaked slide (via TechPowerUp) was supposedly taken from a Lenovo Thinkpad roadmap presentation and shows a release window of around mid-September to the end of October 2020 for Tiger Lake and Lakefield chips. This leak has not been confirmed, but given that Lakefield has been a long time in the works, and that we’ve already seen many hints that Tiger Lake processors are being tested, the timeframe would make sense.

While Tiger Lake CPUs will bring new technologies with them – the most exciting of which perhaps being the inclusion of Intel Xe Gen12 graphics – even more exciting is what Lakefield could provide: a mass-market, consumer-level experiment for Intel’s own take on die stacking.

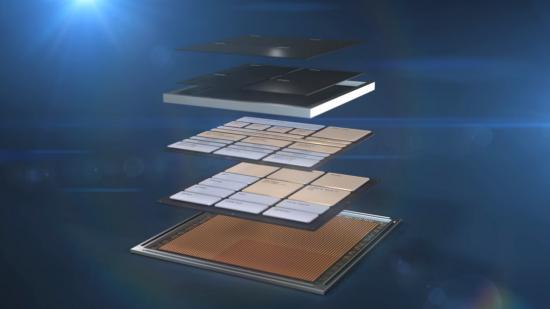

Intel’s Lakefield processors should use its Foveros packaging technology. This design essentially stacks silicon dies atop one another, allowing the base logic die to connect face-to-face with I/O, memory, and other logic dies, amongst other things, connecting them vertically with through-silicon-vias (TSVs). This is why the technology is sometimes called ‘3D’ (as in the leaked Lenovo slide): it allows interconnects through both vertical and horizontal planes.

We’ve seen the move towards more inventive packaging and interconnect technology already with AMD’s ‘Infinity Fabric’ holding its chiplet design together – a HyperTransport technology that allows for super fast transfer speeds, somewhat alleviating the latency caused by breaking a CPU up into different chiplets. And now it looks like Intel will be having a go at new ways of interconnecting more than just base CPU cores, putting an entire system of Foveros-packaged components on top of one another to form its Mobile Lakefield SoC.

This will also be a good opportunity to really put Intel’s own die stacking to the test. Next-next gen Intel Alder Lake-S CPUs are rumoured to combine ‘big’ and ‘little’ cores just like in ARM’s big.LITTLE architecture, and what better way to interconnect them than by stacking them face-to-face? Alder Lake-S CPUs to be big.LITTLE and die stacked? Surely not. But considering Alder Lake-S is expected to debut in late 2021 or early 2022, Intel would have plenty of time to trial the interconnect design with Lakefield… I’ll believe it when I see it.