Much to Intel’s chagrin, Samsung is now the biggest semiconductor manufacturer in the world, and has been busy laying out its plans for process domination right down to the 3nm level. That’s got to really stick in the silicon craw of their rivals, with Intel still struggling to get their 10nm manufacturing to a workable stage. Poor loves.

Samsung disclosed the details of its process roadmap at the 3rd Annual US Samsung Foundry Forum, where the company laid out its plans to give us all “insight in new and previously unthought-of ways to make human lives better.” This level of process shrinking could keep Samsung right at the front of semiconductor manufacturing for generations to come.

We love silicon, especially when it’s powering the best graphics cards around today.

Samsung has scheduled the first ever EUV semiconductor process to go into production in the second half of this year, with actual products likely to appear in the first half of 2019. That’s ahead of the 2020 target for Samsung’s 7nm EUV we previously expected.

Extreme Ultraviolet lithography (EUV) is key to getting our increasingly complex chips built on ever smaller production processes, and is expected to simplify the manufacturing, and hopefully cost, of future silicon designs. We’ve covered how important EUV is to the next generations of 7nm Intel and AMD processors before, but it’s interesting to see Samsung getting its own EUV manufacturing on track so early.

But being so early, it’s unlikely Samsung will be utilising complete EUV production across a full design on its upcoming 7nm node. Global Foundries has already been on record saying that its first EUV node would only use the burgeoning lithography for ‘non-critical roles’ to being with.

The rest of Samsung’s roadmap is a lot lighter on actual timings, with the prospective 5nm, 4nm, and 3nm nodes only really hinted at.

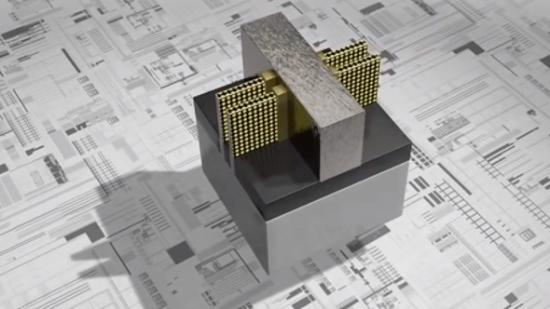

That said, it hasconfirmed the company’s 4nm node will be the last to feature the 3D transistors known as FinFET, with the subsequent 3nm designs using a process called Gate-All-Around. This is to get around the scaling and performance limitations of using the FinFET design at ever smaller, physics-warping, sizes.