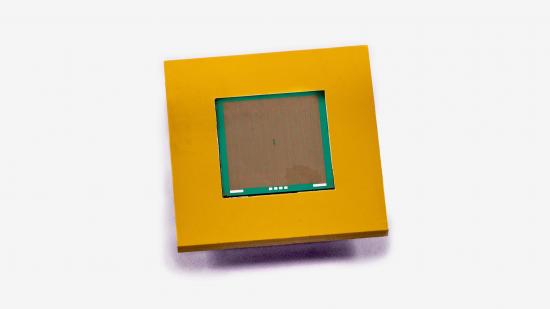

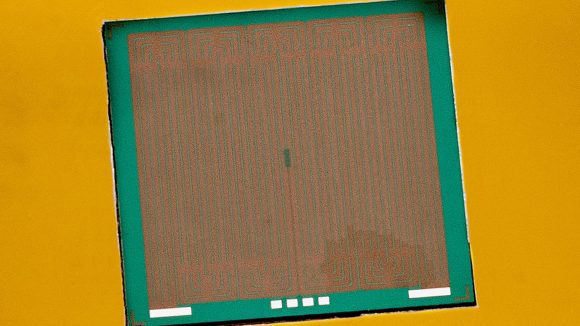

Belgian company Imec has proposed an effective CPU cooler crafted out of silicon and only a couple hundred micrometres deep. This microchannel chiller is capable enough to dissipate massive quantities of heat from its relatively low square-footage, plenty enough for current CPU or GPU designs, and could even reside inside the chip itself.

With a growing need for compute power, the energy efficiency of today’s CPUs and graphics cards is more crucial than ever to their eventual implementation. There’s a tradeoff for all that power within a single package, after all: waste heat. And current cooling methods are exponentially larger than the chips themselves in order to dissipate enough heat for smooth operation.

But Imec has proposed a solution over at the Embedded World Conference 2019 (via HardwareLuxx). Built from silicon, its tiny chip chiller features miniscule channels just 32μm x 260μm big, and these are capable of cooling up to 600W/cm2 at under 100°C. Even Nvidia’s RTX 2080 Ti could be a potential candidate – its 754mm2 die necessitating just a 260W TDP. And the company aims for a price tag of just one dollar a piece.

“It allows for an increase in heat flux by two orders of magnitude compared to classical metal heat sinks,” Philippe Soussan, principal member of the technical staff, says. “Imec is working towards developing a next generation of this chip cooling solution, directly integrating the heat sinks and the IC at wafer scale, aiming at an additional cost of one USD.”

This tech could be put to good use now that Intel, TSMC, and even AMD are all talking chip stacking.

Related: These are the best graphics cards right now

TSMC put forward its own stacking tech last year called Wafer on wafer (WoW), which allows it to pile chips up on top of one another – similar to how HBM memory is many die stacked atop of one another. Each individual chip would be connected via through-silicon-vias (TSVs), allowing for speedy, high-bandwidth interconnectivity.

Intel similarly has put forward its own stacking technology, Foveros. It plans on incorporating TSVs into its chip IO, allowing for chips to be mounted on top of this layer, incorporating more tech into less space. The first SoC built using Foveros technology will be Lakefield, which, once paired with storage, peripherals, and IO, will become Project Athena: fully-fledged PCs just 11-inches big.

And AMD, which hasn’t yet spoken in-depth about any stacking technology but its datacentre VP has made it very clear that the company is going in that direction.

“We’re already at the point where today’s CPUs, the packages, are pretty darned close to the size of the original iPhone,” Forrest Norrod, senior vice president and GM of AMD’s datacentre group, says. “They’re huge. You can’t get any more area in two dimensions, so what do you have to do? You go up.”

While stopping short of high-performance logic on top of logic, a chip of that description seems a near-certainty at this point. All that waste heat will need to be dealt with efficiently to make this approach feasible, and a cooler like Imec’s, while a significant departure from how we package semiconductors today, could be a potential solution for a vertical future.