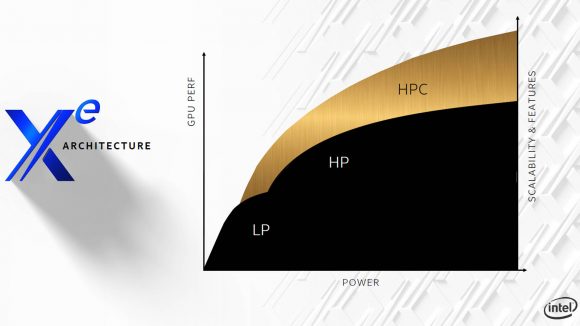

Intel has announced three microarchitectures under the Intel Xe graphics umbrella: Xe-LP, Xe-HP, and Xe-HPC. At the top Xe-HPC, the supercomputer-class GPU fit for the Aurora supercomputer – but it’s the two GPU microarchitectures below, Xe-LP and Xe-HP, that will be of most interest to PC gamers.

Over at DevCon, Intel announced the three sub-tiers of its Xe architecture – ranging from integrated and entry-level graphics cards to supercomputer silicon. It’s all technically the same GPU architecture, but Intel intends on divvying up the functionality and features across the entire product stack.

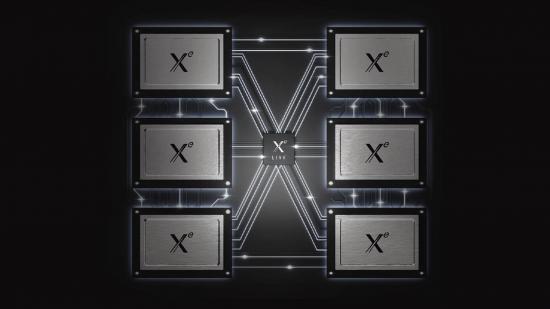

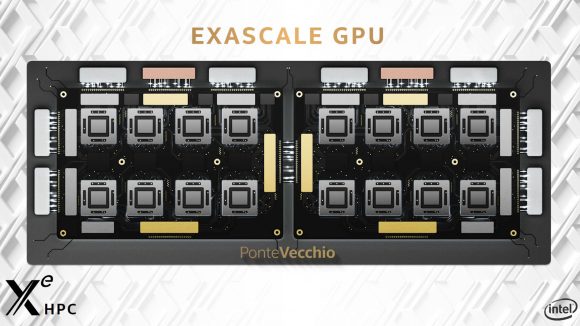

Most of the Xe information disclosed by Intel at DevCon expands on what we know about Intel’s Ponte Vecchio GPU. Intel intends on using Xe Link, based on the standards laid out by the CXL consortium (whose members include AMD and Nvidia), to scale its 7nm Xe GPU up to exascale performance. Today, Intel is touting an architecture capable of scaling to “thousands of execution units.”

Execution units are the basis for all of Intel’s graphics ventures so far, including Gen9 graphics within the best CPUs for gaming today and the Gen11 graphics in its recently released mobile Ice Lake SoCs. These currently top out at 64EUs.

Intel Xe-HP appears to be intended for the professional and data centre market, while Xe-LP would likely fit into a discrete GPU for the gaming market. It is suspected that Intel’s code name DG1 refers to Gen12LP, while DG2 is Gen12HP.

Intel Xe-HPC will also support INT8, BF16, and FP16 data types via its “data parallel Matrix Engine.” Perhaps similar in nature to Nvidia’s Tensor Cores, this Matric Engine will chomp through AI inference tasks. Intel also supports many of these data types across its current Xeon server CPU lineup.

Another Xe-HPC feature announced is a scalable memory fabric connecting GPU and CPU compute altogether with access to a unified coherent memory. Intel is touting this interconnecting cache, expertly-named Rambo Cache, between Intel Xe compute cores and HBM (high bandwidth memory). For Ponte Vecchio, Intel’s EMIB technology will connect up HBM to chip, while Rambo Cache will utilise Intel’s Foveros stacking technology.

It’s unlikely that Intel will opt for pricey HBM memory for entry-level and enthusiast cards on the Xe-LP microarchitecture.

Unfortunately, beyond the names Xe-LP and Xe-HP, there’s little more on Intel’s client-side GPUs or microarchitectures. We can so far only guess which, if any, of the features listed above will trickle down into gaming graphics cards.

The first graphics cards from Chipzilla are expected in 2020, and we know Intel intends to scale up to the Aurora supercomputer in 2021 with its Ponte Vecchio GPU announced last Sunday at Supercompute ‘19. Ponte Vecchio won’t be all that similar to Intel’s gaming Xe fare, however, and will be built using the company’s 7nm process and Foveros 3D packaging technology.